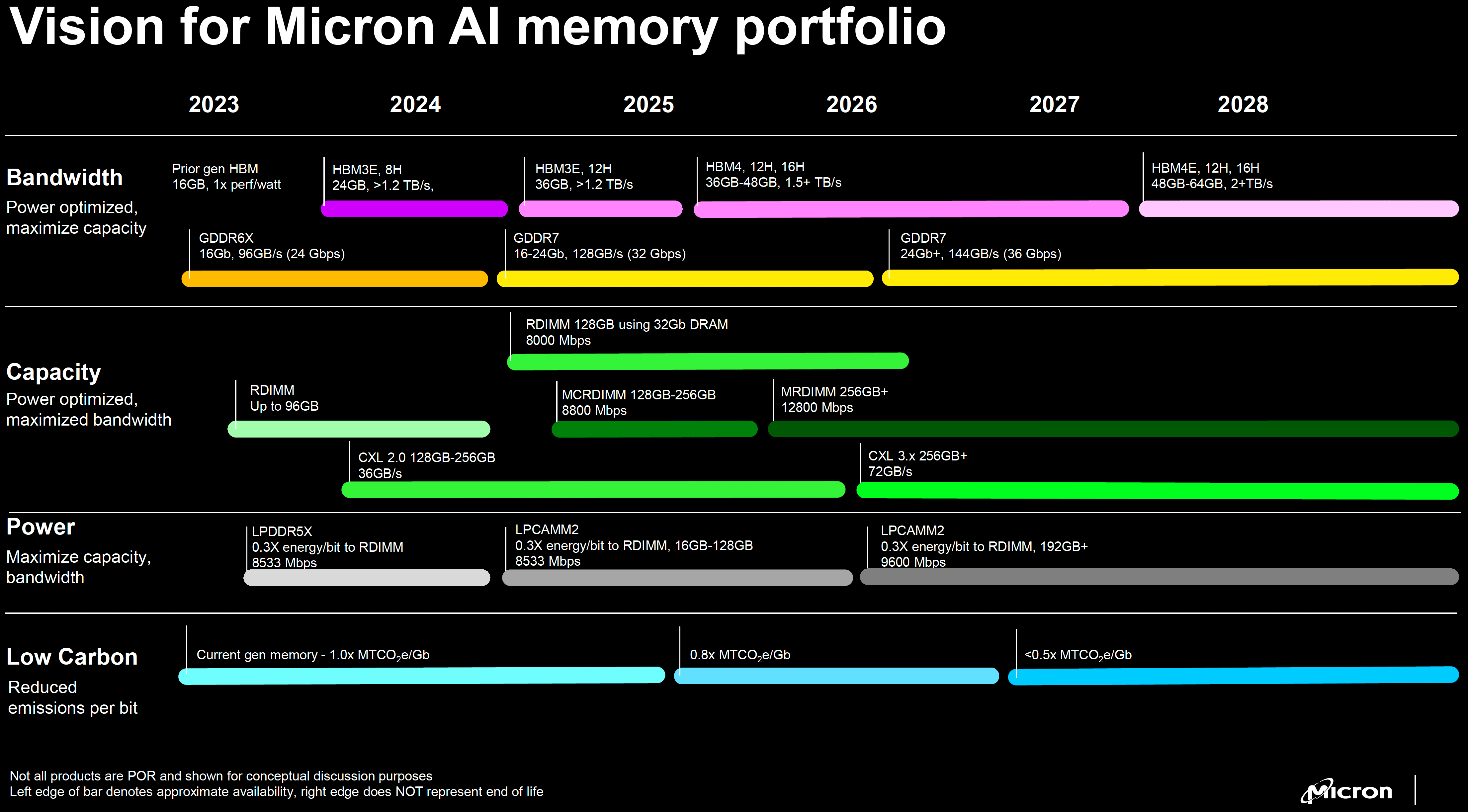

Esta semana, a Micron forneceu uma atualização sobre seus programas HBM4 e HBM4E. A memória HBM4 de próxima geração, com interface de 2.048 bits, está a caminho da produção em massa no ano civil de 2026, com HBM4E nos anos subsequentes. Além de oferecer taxas de transferência de dados mais altas do que o HBM4, o HBM4E também introduzirá uma opção para personalizar sua matriz base, marcando uma mudança de paradigma para a indústria.

Sem dúvida, o HBM4 impressiona pela sua interface de memória de 2.048 bits. No entanto, o HBM4E será ainda mais impressionante, permitindo à Micron oferecer matrizes de base personalizadas para determinados clientes, fornecendo assim soluções mais otimizadas com recursos potencialmente adicionais. As matrizes lógicas personalizadas são configuradas para serem feitas pela TSMC usando um nó avançado, permitindo-lhes empacotar mais caches e lógica para desempenho e funcionalidade adicionais.

“A HBM4E introduzirá uma mudança de paradigma no negócio de memória ao incorporar uma opção para personalizar a matriz lógica para determinados clientes usando um processo avançado de fabricação de fundição lógica da TSMC”, disse Sanjay Mehrotra, presidente e CEO da Micron. “Esperamos que esta capacidade de personalização melhore o desempenho financeiro da Micron.”

Por enquanto, só podemos nos perguntar como a Micron planeja personalizar suas matrizes lógicas básicas HBM4E. Ainda assim, a lista de possibilidades é longa e inclui recursos básicos de processamento, como caches aprimorados, protocolos de interface personalizados adaptados para aplicações específicas (IA, HPC, rede, etc.), capacidades de transferência de memória para memória, larguras de interface variáveis, tensão avançada dimensionamento e controle de energia e ECC personalizado e/ou algoritmos de segurança. Lembre-se de que isso é especulativo. Neste ponto, ainda não está claro se um padrão JEDEC real suporta tais personalizações.

A Micron afirma que o trabalho de desenvolvimento dos produtos HBM4E está bem encaminhado com vários clientes, portanto, podemos esperar que diferentes clientes adotem matrizes básicas com configurações diferentes. Isso marca um passo em direção a soluções de memória personalizadas para IA, HPC, redes e outras aplicações que exigem muita largura de banda. Ainda não se sabe como as soluções personalizadas HBM4E se comparam às soluções personalizadas HBM (cHBM4) da Marvell, lançadas no início deste mês.

O HBM4 da Micron usará as DRAMs da empresa feitas em seu comprovado 1β (tecnologia de processo de classe 10 nm de 5ª geração), colocado no topo de uma matriz base com uma interface ampla de 2.048 bits e uma taxa de transferência de dados de cerca de 6,4 GT/s, que irá fornecem uma largura de banda teórica de pico de 1,64 TB/s por pilha. A Micron planeja aumentar a produção de HBM4 em alto volume no ano civil de 2026, o que se alinha com o lançamento das GPUs Vera Rubin da Nvidia e das GPUs da série Instinct MI400 da AMD para aplicações de IA e HPC. Curiosamente, há rumores de que tanto a Samsung quanto a SK Hynix usam tecnologia de fabricação de classe 10nm de 6ª geração para seus produtos HBM4.

A Micron também revelou esta semana que as remessas de seus dispositivos 8-Hi HBM3E para os processadores Blackwell da Nvidia já estão a todo vapor. As pilhas 12-Hi HBM3E da empresa estão sendo testadas por seus principais clientes, que estão satisfeitos com os resultados.

“Continuamos recebendo feedback positivo de nossos principais clientes sobre as pilhas HBM3E 12-Hi da Micron, que apresentam o melhor consumo de energia da categoria – 20% menor que o HBM3E 8-Hi da concorrência – mesmo que o produto Micron ofereça memória 50% maior. capacidade e desempenho líder do setor”, disse Mehrotra.

Espera-se que as pilhas 12-Hi HBM3E sejam usadas pelos aceleradores Instinct MI325X e MI355X da AMD, bem como pelas GPUs de computação da série Blackwell B300 da Nvidia para cargas de trabalho de IA e HPC.